こんにちは。ソリューション開発課の宮田です。3回目の執筆となりました。本コラムでは、特注製品開発における経験談の一つをお話しします。よろしくお願いいたします。

本製品は安全関連試験機器「TOSシリーズ」を改造した特注品です。内容は、直流のみの耐電圧試験、絶縁抵抗試験の2つの試験に特化したローコスト製品です。またこの特注品の特筆すべきは、被試験物が二次電池ということでした。二次電池の試験は一般の家電品などと違い、蓄えられた電気エネルギーが試験用ケーブルを通じて試験器に供給されることが想定できます。したがってそのエネルギー量によっては試験器の故障・破損につながる恐れがあるのです。

被試験物(二次電池)の短絡保護が必要

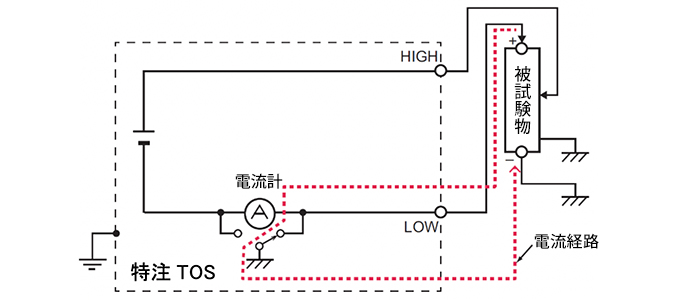

二次電池を被試験物とした場合に、接続や設定によって被試験物から本製品へ過電流が流れ込み被試験物を短絡することがあります(図1)。

(図1)特注TOSのLOW側ケーブルとグランドにより被試験物が短絡

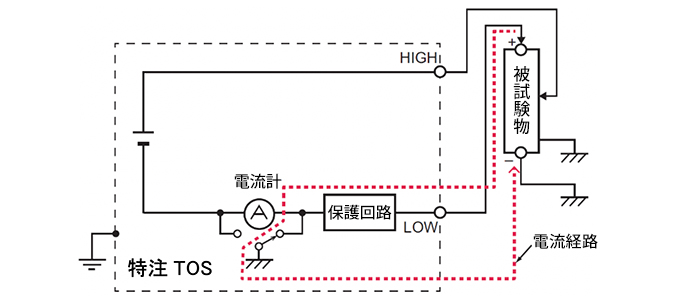

この過電流を検出し電流を制限する保護回路を設計することが重要なポイントです(図2)。

(図2)特注TOSのLOW側内部に保護回路を挿入

高電圧に耐える双方向定電流回路

今回のミッションは、数kVという高電圧で使用可能な保護回路、つまり双方向定電流回路を低コストで設計する事だとわかりました。そこで、MOS FETを使った定電流回路を検討する事にしました。さっそく実際に回路を構成し検証してみると、MOS FETのブレークダウン電圧までは問題なく動作するものの、印加電圧を増やしていき、ブレークダウン電圧の2倍程度の電圧を加えたとたんにMOS FETが壊れてしまい、定電流制御をしなくなってしまいました(図3)。

(図3)抵抗器による分圧だけの回路

課題は素子電圧の不平衡

MOS FETの多段直列接続で高電圧の回路を作る場合の注意点があります。各MOS FETのスイッチイングタイミングに差が生じたとき、各MOS FETの素子電圧が不平衡となり、特定のMOS FETに過大な電圧責務がかかることがあります。つまり素子電圧の不平衡を抑制することが、MOS FETを直列接続する際の最大の課題なのです。しかし、この時点で私はそのことに気づいていませんでした。

先に作った実験回路では、定電流の動作は問題ないが耐電圧の問題が解決できません。そこで直列段数を増やすなどを実施し、耐電圧を増やしてみましたが、それでは素子毎の電圧アンバランスの解消にはならず、当然壊れてしまい頭を抱えていました。 こういったときは、素直にお助けマンを呼ぶのが正解です。諸先輩たちからご意見を頂く中で、MOS FETの寄生容量の話しを聞き、寄生容量を無視すれば良いということを知りました。そこで寄生容量を無視できるようなコンデンサーを実装し再検証を行いました(図4)。

(図4)ゲート-ドレイン間に電圧バランス用コンデンサーを追加した回路

電圧バランスのキーパーツはコンデンサー

MOS FETの寄生容量は、印加される電圧や温度によって変化します。最初に検討したMOS FETの定電流回路(図3)では、寄生容量の変化(ばらつき)が各段に印加される電圧のアンバランスを生み、結果として1つのMOS FETに大きな電圧が印加されて破壊に至ったわけです。

しかし再検討した回路(図4)では、電圧バランス用にコンデンサーを追加することで、寄生容量による電圧印加時の容量変動はなくなり、高電圧を印加しても壊れなくなり、簡易的な高電圧、双方向定電流回路を完成させることができました。コスト面でも、通常の高耐圧部品の約1/4倍の金額となり、大幅な仕様を変更なしに、しかもローコストで実現することができました。

あたらめて部品の基本特性を確認しよう

何かにつまずいた時にまず行うのは、部品仕様や性能、特性を冷静に再確認することが重要だと感じました。それが出来ていれば今回の悩みは早期に解決したのかもしれません(MOS FETの寄生容量の変化はFETの基本特性です)。

今回も先輩の助言から気づきを得て、なんとか解決できましたが、そろそろ1人で解決できなくてはと痛感しました。それには、どんな時でも焦らず冷静に物事を考え、推測し、実行できるようになりたいと思いました。

本案件は、少し開発スケジュールをオーバーする状況でしたが、機能は十分、コストも抑えた回路が完成したことに、上司から労いの言葉「お疲れ様でした」を頂くことができました。

これからも知識と経験をどんどん蓄積させて、エンジニアとして進化して行きたいと思うこの頃です。